- #DOWNLOAD QUARTUS II WEB EDITION 2016 HOW TO#

- #DOWNLOAD QUARTUS II WEB EDITION 2016 PDF#

- #DOWNLOAD QUARTUS II WEB EDITION 2016 INSTALL#

- #DOWNLOAD QUARTUS II WEB EDITION 2016 SOFTWARE#

- #DOWNLOAD QUARTUS II WEB EDITION 2016 DOWNLOAD#

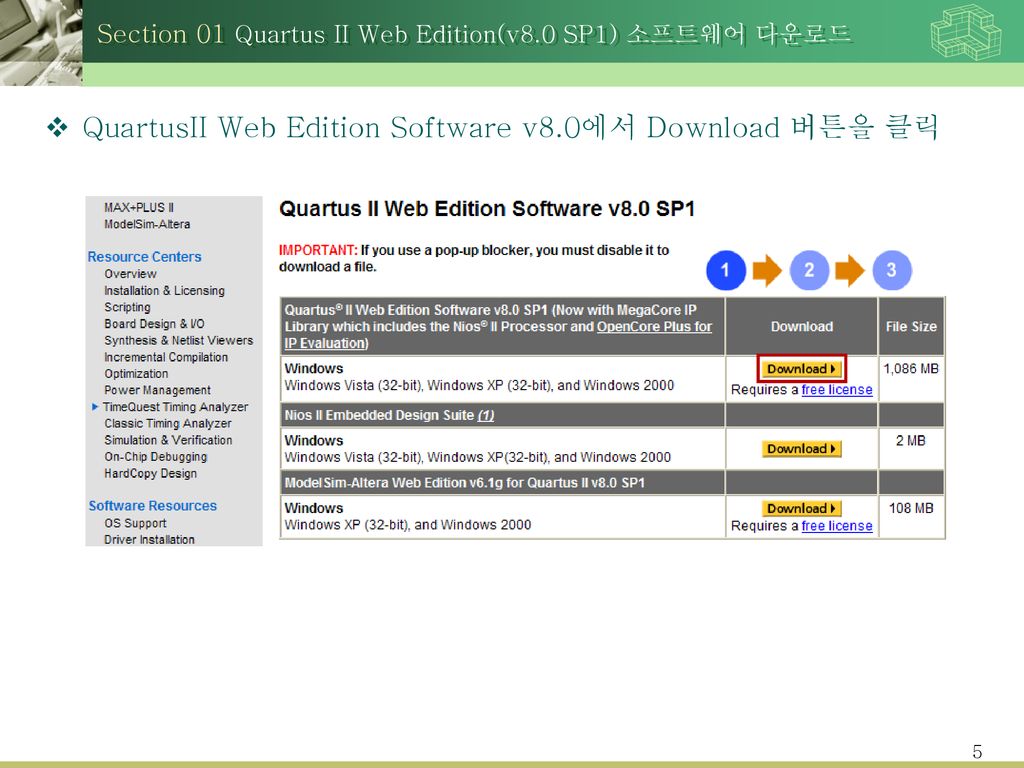

Make sure you tick the box to download the MAX7000 device support.

#DOWNLOAD QUARTUS II WEB EDITION 2016 INSTALL#

Download and install a version of Quartus II that supported the MAX7000 series (ie version 13.0 SP 1).The process is documented in Atmel’s Application Note 0916.

#DOWNLOAD QUARTUS II WEB EDITION 2016 SOFTWARE#

It has been mentioned to me that an old version of Altera’s Quartus II software can be used to develop in Verilog or VHDL to target the Atmel ATF1508AS device. Nandland’s page on tri-state outputs in Verilog.

#DOWNLOAD QUARTUS II WEB EDITION 2016 HOW TO#

Youtube video: How to create a Quartus Prime project from scratch and assign pins for the DE10-Lite NandLand’s Verilog Totorials and Examples However, they can only sink 40mAwith an output voltage of 0.7V. The datasheet for the 7438 is here.Ī 7406 or 7407 could probably also be used to drive the bus 9they both have open-collector outputs). Its an open-collector 4 x NAND gate, with a maximum output voltage of 0.4V when sinking a 48mA load. The “omniusb” prject uses 7438’s to drive the bus.

#DOWNLOAD QUARTUS II WEB EDITION 2016 PDF#

Vince’s webpage is here, and the PDF of the schematic is here. In 2014, Vince put together a 32K RAM board based on Steve’s design. It is commonly thought that the 8881 is a DEC-rebranded 7439. Output voltage is typically 0.4-0.6 (maximum 0.8V) when sinking 50mA.

The cookie is used to store the user consent for the cookies in the category "Performance". This cookie is set by GDPR Cookie Consent plugin. The cookie is used to store the user consent for the cookies in the category "Other. The cookies is used to store the user consent for the cookies in the category "Necessary". The cookie is set by GDPR cookie consent to record the user consent for the cookies in the category "Functional".

The cookie is used to store the user consent for the cookies in the category "Analytics".

These cookies ensure basic functionalities and security features of the website, anonymously. Necessary cookies are absolutely essential for the website to function properly. Subscribe to EDN's monthly IC/FPGA Design newsletter ( free registration) for the latest product announcements and news. More information about the Spectra-Q engine at įind more datasheets on products like this one at, searchable by category, part #, description, manufacturer, and more.ĭon't miss out on the latest products. The new engine is integrated in the Quartus-II Software and IP, Version 15.0, just released.īoth the Subscription Edition and the free Web Edition of the Quartus II software v15.0 are now available for download at. In addition to providing support for the latest HDLs, the new engine is designed to support Altera’s new A++ Compiler for HLS (high level synthesis) to create IP cores from C or C++ which significantly boosts productivity through faster simulation and IP generation. The tool also includes a clock and core planning feature that greatly reduces the number of design iterations needed for timing closure. The tool reduces design iterations by 10× by allowing designers to explore and create legal IO placements up-front with real-time fitter-checking. This helps ensure stable designs, eliminates unnecessary timing closure efforts and reduces compile times.īuilt on top of the Spectra-Q engine is a platform design tool called BluePrint that allows designers to perform architectural exploration and assign interfaces with greater efficiency. It also features a hierarchical database that enables users to preserve placement and routing information of IP blocks while making changes in other parts of the design.

0 kommentar(er)

0 kommentar(er)